#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

## (19) World Intellectual Property Organization

International Bureau

(43) International Publication Date

#

(10) International Publication Number WO 2012/176081 A1

27 December 2012 (27.12.2012)

(21) International Application Number:

(51) International Patent Classification:

PCT/IB2012/052709

(22) International Filing Date:

H01L 25/065 (2006.01)

30 May 2012 (30.05.2012)

H04B 5/00 (2006.01)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

1101902 21 June 2011 (21.06.2011)

FR

(71) Applicant (for all designated States except US): TEKCEM [FR/FR]; 12 chemin des Hauts de Clairefontaine, F-78580 Maule (FR).

(72) Inventors; and

(75) Inventors/Applicants (for US only): BROYDE, Frederic [FR/FR]; 12 chemin des Hauts de Clairefontaine, F-78580 Maule (FR). CLAVELIER, Evelyne [FR/FR]; 12 chemin des Hauts de Clairefontaine, F-78580 Maule (FR).

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ,

CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### Published:

- with international search report (Art. 21(3))

- before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments (Rule 48.2(h))

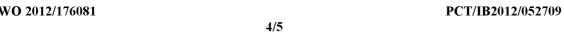

(57) Abstract: The invention relates to a transmitter for a near-field chip-to-chip multichannel transmission system such as the capacitive or inductive links used for vertical signal transmission between the stacked chips of a system-in-package. A transmitter for near-field chip-to-chip multichannel transmission providing 4 transmission channels for digital transmission between two monolithic integrated circuits comprises 4 coupling devices (111) (112) (113) (114), each of said coupling devices being a planar winding sensitive to magnetic field variations. A multiple-input-port and multiple-output- port amplifier (13) has 4 output ports, each of said output ports being connected to one and only one of said coupling devices (111) (112) (113) (114). The transmitter also comprises 4 signal shaping circuits (181) (182) (183) (184), each of said signal shaping circuits having an input port connected to the source (19), each of said signal shaping circuits having an output port connected to one of the input ports of the multiple-input-port and multiple-output-port amplifier (13). The transmitter of the invention reduces crosstalk between the transmission channels.

FIG. 4

WO 2012/176081 PCT/IB2012/052709

## Transmitter for near-field chip-to-chip multichannel transmission

## FIELD OF THE INVENTION

The invention relates to a transmitter for a near-field chip-to-chip multichannel transmission system such as the capacitive or inductive links used for vertical signal transmission between the stacked chips of a system-in-package (SiP) using three-dimensional (3-D) integration.

The French patent application number 11/01902 of 21 June 2011, entitled "Emetteur pour transmission multivoie puce-à-puce en champ proche" is incorporated by reference.

## PRIOR ART

5

10

15

20

25

30

35

Three-dimensional integration is a new technology that enables an effective integration of complex systems. In a package using three-dimensional integration, chips may be stacked and structurally combined. In such a system-in-package, the vertical distance for signal transmission between two chips is typically smaller than 200 µm. Many vertical chip-to-chip transmission techniques have been developed. Techniques using through-silicon vias (TSVs) are expensive due to the increase of manufacturing process complexity. Techniques using near-field chip-to-chip transmission do not increase the process complexity.

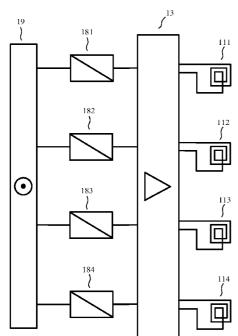

The Fig. 1 shows the coupling devices of a near-field chip-to-chip multichannel transmission system providing m = 12 transmission channels between a first monolithic integrated circuit (1) and a second monolithic integrated circuit (2), the near-field chip-to-chip multichannel transmission system comprising:

- a first array of coupling devices (11) built in a metallization level of the first monolithic integrated circuit (1), a coupling device (111) of the first array of coupling devices (11) being sensitive to electric field variations and/or to magnetic field variations, the first array of coupling devices (11) consisting of *m* coupling devices;

- a second array of coupling devices (21) built in a metallization level of the second monolithic integrated circuit (2), a coupling device (211) of the second array of coupling devices (21) being sensitive to electric field variations and/or to magnetic field variations, the second array of coupling devices (21) consisting of *m* coupling devices, a coupling device (211) of the second array of coupling devices (21) facing a single coupling device (111) of the first array of coupling devices (11).

A coupling device sensitive to electric field variations, for instance a conducting surface having a sufficient area (referred to as a capacitor plate by some authors), can be used for receiving an electric field used for signal transmission and can also be used for sending an electric field used for signal transmission. A coupling device sensitive to magnetic field

variations, for instance a winding (referred to as coil or inductor by some authors), can be used for receiving a magnetic field used for signal transmission and can also be used for sending a magnetic field used for signal transmission. More generally, a coupling device may be any device sensitive to electric field variations and/or to magnetic field variations, for instance a device comprising a combination of conducting surfaces and/or of windings.

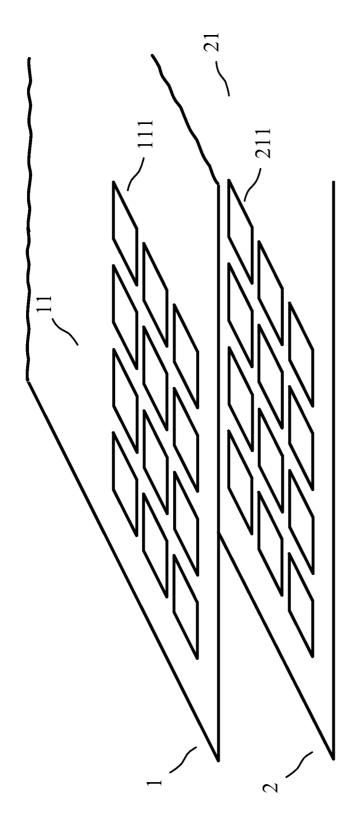

The Fig. 2 shows the block-diagram of a first example of a transmitter of a near-field multichannel transmission system providing m = 4 transmission channels for digital transmission between two monolithic integrated circuits, comprising:

5

10

15

25

30

35

m signal shaping circuits (181) (182) (183) (184), each of said signal shaping circuits having an input port connected to the source (19);

- m single-ended input and single-ended output amplifiers (121) (122) (123) (124), each single-ended input and single-ended output amplifier having its input terminal connected to the output terminal of one and only one signal shaping circuit (181) (182) (183) (184);

- m coupling devices (111) (112) (113) (114), each coupling device being a planar winding sensitive to magnetic field variations, each coupling device having a first terminal and a second terminal, the first terminal being connected to the output terminal of one and only one single-ended input and single-ended output amplifier (121) (122) (123) (124), the second terminal being grounded.

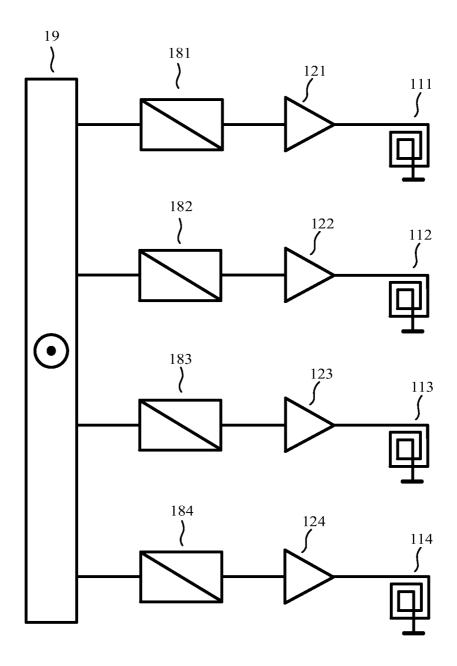

- The Fig. 3 shows the block-diagram of a second example of a transmitter of a near-field multichannel transmission system providing m = 4 transmission channels for digital transmission between two monolithic integrated circuits, comprising:

- m signal shaping circuits (181) (182) (183) (184), each of said signal shaping circuits having an input port connected to the source (19);

- m differential input and differential output amplifiers (121) (122) (123) (124), each differential input and differential output amplifier having an input port connected to the output port of one and only one of said signal shaping circuits (181) (182) (183) (184);

- m coupling devices (111) (112) (113) (114), each coupling device being a planar winding sensitive to magnetic field variations, each coupling device having a first terminal and a second terminal, the first terminal and the second terminal being connected to the output port of one and only one differential input and differential output amplifier (121) (122) (123) (124).

In the figures 2 and 3, the signal shaping circuits deliver signals which are suitable for the chosen signaling technique. A signal shaping circuit can use different types of circuits, which are well known to specialists. For instance, a signal shaping circuit may generate pulses corresponding to one of the pulse code modulation (PCM) formats. For instance, a signal shaping circuit may generate a modulated carrier. The enable and/or clock and/or control lines which may be necessary for the operation of the signal shaping circuits are not shown in the figures 2 and 3.

Even though each coupling device may be considered as an electrically small antenna in the meaning of antenna theory, it is important to note that, in a near-field chip-to-chip multichannel transmission system, an array of coupling devices is not used as an array of antennas in the meaning of antenna theory. This is because the array of coupling devices operates in a near-field transmission system in which the electric and magnetic fields decrease very rapidly with distance. Thus, in an ideal case, a coupling device used for receiving an electric field and/or a magnetic field only senses the electric field and/or magnetic field variations produced by the nearest coupling device used for sending an electric field and/or a magnetic field. For instance, in Fig. 1 where a coupling device (211) of the second array of coupling devices (21) faces a single coupling device (111) of the first array of coupling devices (11), it is possible that signal transmission mainly occurs between coupling devices facing each other, either from the first monolithic integrated circuit (1) to the second monolithic integrated circuit (2), or from the second monolithic integrated circuit (2) to the first monolithic integrated circuit (1).

However, some unwanted couplings unavoidably occur, which produce crosstalk between the transmission channels. Unfortunately, this internal crosstalk limits the number of channels which can be used in a given area. This internal crosstalk has three causes:

- a coupling device of one of the arrays of coupling devices may be significantly coupled with more than one coupling device of the other array of coupling devices, because signal transmission does not only occur between coupling devices facing each other;

- the coupling devices of the first array of coupling devices interact;

10

15

20

25

30

35

- the coupling devices of the second array of coupling devices interact.

For instance, the article of A. Fazzi, L. Magagni, M. Mirandola, B. Charlet, L. Di Cioccio, E. Jung, R. Canegallo and R. Guerrieri entitled "3-D Capacitive Interconnections for Wafer-Level and Die-Level Assembly" published in the *IEEE Journal of Solid-State Circuits*, vol. 42, No. 10, pp. 2270-2282 in October 2007 relates to a near-field chip-to-chip multichannel transmission system using electric field variations for signal transmission. This paper discusses crosstalk between the transmission channels.

For instance, the article of Y. Yoshida, N. Miura and Tadahiro Kuroda entitled "A 2 Gb/s Bi-Directional Inter-Chip Data Transceiver With Differential Inductors for High Density Inductive Channel Array" published in the *IEEE Journal of Solid-State Circuits*, vol. 43, No. 11, pp. 2363-2369 in November 2008 relates to a near-field chip-to-chip multichannel transmission system using magnetic field variations for signal transmission. This paper stresses the detrimental effects of crosstalk and introduces the use of special windings, referred to as "differential inductors", for reducing crosstalk. Unfortunately, such special windings produce a lower wanted coupling for a given area and provide only a partial reduction of crosstalk.

## SUMMARY OF THE INVENTION

10

15

20

25

30

35

The purpose of the invention is a transmitter for near-field chip-to-chip multichannel transmission which overcomes the above-mentioned limitations of known techniques.

According to the invention, a transmitter of a near-field multichannel transmission system providing m transmission channels each corresponding to a signal to be sent from a first monolithic integrated circuit to a second monolithic integrated circuit, where m is an integer greater than or equal to 2, the first monolithic integrated circuit and the second monolithic integrated circuit being structurally combined, comprises n coupling devices built in the first monolithic integrated circuit, where n is an integer greater than or equal to m, each of said coupling devices being subject to an electrical variable determined by two or more of said signals to be sent. According to the invention, each of said coupling devices is sensitive to electric field variations and/or to magnetic field variations. According to the invention, the electrical variable applied to one of said coupling devices may be a voltage or a current.

According to the invention, a transmitter of a near-field multichannel transmission system providing m transmission channels each corresponding to a signal to be sent from a first monolithic integrated circuit to a second monolithic integrated circuit, where m is an integer greater than or equal to 2, the first monolithic integrated circuit and the second monolithic integrated circuit being structurally combined may for instance comprise:

n coupling devices built in the first monolithic integrated circuit, where n is an integer greater than or equal to m, each of said coupling devices being sensitive to electric field variations and/or to magnetic field variations;

a multiple-input-port and multiple-output-port amplifier, said multiple-input-port and multiple-output-port amplifier being built in the first monolithic integrated circuit, said multiple-input-port and multiple-output-port amplifier having m input ports and n output ports, each of said output ports being connected to one and only one of said coupling devices, each of said coupling devices being connected to one and only one of said output ports, said multiple-input-port and multiple-output-port amplifier having, when said multiple-input-port and multiple-output-port amplifier is in the activated state, for small signals, at each frequency in a frequency band used for transmission, a short-circuit transfer admittance matrix, said short-circuit transfer admittance matrix being a complex matrix of size  $n \times m$ , two or more entries of each row of said short-circuit transfer admittance matrix being different from zero.

Let us number, from 1 to m, the input ports of the multiple-input-port and multiple-output-port amplifier. Any integer j greater than or equal to 1 and less than or equal to m corresponds to the number of an input port of the multiple-input-port and multiple-output-port amplifier. Let us define the input current  $i_{Ij}$  flowing into the positive terminal of the input port j, and the input voltage  $v_{Ij}$  between the positive terminal of the input port j and the negative

terminal of the input port j. We also define the column-vector  $\mathbf{I}_I$  of the input currents  $i_{I1}, ..., i_{Im}$  and the column-vector  $\mathbf{V}_I$  of the input voltages  $v_{I1}, ..., v_{Im}$ . Let us number, from 1 to n, the output ports of the multiple-input-port and multiple-output-port amplifier. Any integer k greater than or equal to 1 and less than or equal to n corresponds to the number of an output port of the multiple-input-port and multiple-output-port amplifier. Let us define the output current  $i_{Ok}$  flowing into the positive terminal of the output port k, and the output voltage  $v_{Ok}$  between the positive terminal of the output port k and the negative terminal of the output port k. We also define the column-vector  $\mathbf{I}_O$  of the output currents  $i_{O1}, ..., i_{On}$  and the column-vector  $\mathbf{V}_O$  of the output voltages  $v_{O1}, ..., v_{On}$ . When the multiple-input-port and multiple-output-port amplifier is in the activated state, for small signals, the multiple-input-port and multiple-output-port amplifier is characterized, in frequency domain, by the two following equations:

10

15

20

25

30

35

$$\mathbf{I}_{I} = \mathbf{Y}_{I} \ \mathbf{V}_{I} + \mathbf{Y}_{R} \mathbf{V}_{O} \tag{1}$$

$$\mathbf{I}_{O} = \mathbf{Y}_{T} \ \mathbf{V}_{I} + \mathbf{Y}_{O} \mathbf{V}_{O} \tag{2}$$

where  $\mathbf{Y}_I$  is a square  $m \times m$  matrix, where  $\mathbf{Y}_O$  is a square  $n \times n$  matrix, where  $\mathbf{Y}_R$  is a  $m \times n$  matrix and where  $\mathbf{Y}_T$  is a  $n \times m$  matrix. All components of these matrices have the dimensions of admittance. Consequently, specialists understand that they can refer to  $\mathbf{Y}_I$  as the "short-circuit input admittance matrix" of the amplifier, to  $\mathbf{Y}_R$  as the "short-circuit reverse transfer admittance matrix" of the amplifier, to  $\mathbf{Y}_T$  as the "short-circuit transfer admittance matrix" of the amplifier, and to  $\mathbf{Y}_O$  as the "short-circuit output admittance matrix" of the amplifier. These four matrices have complex components and may be frequency-dependent.

Two or more entries of each row of said short-circuit transfer admittance matrix may be significantly different from zero. For instance, said multiple-input-port and multiple-output-port amplifier may be such that, at each frequency in said frequency band used for transmission, in each row of said short-circuit transfer admittance matrix, at least one entry different from an entry having the greatest absolute value has an absolute value greater than 1/100 times the absolute value of said entry having the greatest absolute value. For instance, said multiple-input-port and multiple-output-port amplifier may be such that, at each frequency in said frequency band used for transmission, in each row of said short-circuit transfer admittance matrix, at least one entry different from an entry having the greatest absolute value has an absolute value greater than 1/10 times the absolute value of said entry having the greatest absolute value.

In the following, the wordings "is in the deactivated state" and "is not in the activated state" are equivalent.

The multiple-input-port and multiple-output-port amplifier in the activated state has, for small signals, at each frequency in a frequency band used for transmission, a short-circuit transfer admittance matrix, said short-circuit transfer admittance matrix being a complex matrix

of size  $n \times m$ , two or more entries of each row of said short-circuit transfer admittance matrix being significantly different from zero. According to the invention, it is possible that there is a deactivated state of the multiple-input-port and multiple-output-port amplifier, in which the behavior of the multiple-input-port and multiple-output-port amplifier is different. However, the existence of a deactivated state of the multiple-input-port and multiple-output-port amplifier is not at all a characteristic of the invention.

According to the invention, said *n* coupling devices built in the first monolithic integrated circuit are used for sending an electric field and/or a magnetic field, as parts of a near-field transmission system providing *m* transmission channels each corresponding to a signal to be sent from the first monolithic integrated circuit to the second monolithic integrated circuit. Said *n* coupling devices built in the first monolithic integrated circuit can also be used for receiving an electric field and/or a magnetic field, as parts of a near-field transmission system providing one or more transmission channels each corresponding to a signal to be sent from the second monolithic integrated circuit to the first monolithic integrated circuit. Thus, a bidirectional transmission is obtained. The specialist understands how this result can be obtained, for instance using controlled analog switches and/or a deactivated state of the multiple-input-port and multiple-output-port amplifier.

10

15

20

25

30

35

According to the invention, the first monolithic integrated circuit and the second monolithic integrated circuit are structurally combined, so that the first and second monolithic integrated circuits have fixed relative positions. The specialist understands that this requirement allows the designer to compute the effects of the three above-mentioned causes of internal crosstalk, and to determine a set of short-circuit transfer admittance matrices which can each cancel internal crosstalk between the signals delivered by the coupling devices built in the second monolithic integrated circuit.

According to the invention, at least one other monolithic integrated circuit can be structurally combined with the first monolithic integrated circuit and/or the second monolithic integrated circuit. In this case:

- the transmitter of the invention can also be used as a part of a near-field transmission system providing one or more transmission channels each corresponding to a signal to be sent from the first monolithic integrated circuit to said at least one other monolithic integrated circuit;

- the *n* coupling devices built in the first monolithic integrated circuit can also be used for receiving an electric field and/or a magnetic field, as parts of a near-field transmission system providing one or more transmission channels each corresponding to a signal to be sent from said at least one other monolithic integrated circuit to the first monolithic integrated circuit.

The multiple-input-port and multiple-output-port amplifier may for instance be such that the negative terminals of its input ports and/or of its output ports correspond to ground, such ports being single-ended in this case.

The multiple-input-port and multiple-output-port amplifier may for instance be such that

each of its input ports corresponds to a differential input and/or such that each of its output ports corresponds to a differential output.

The multiple-input-port and multiple-output-port amplifier may comprise a multiple-input and multiple-output series-series feedback amplifier, for instance described in the French patent application number 06/00388 of 17 January 2006 entitled "Amplificateur à entrées multiples et sorties multiples", in the corresponding international application number PCT/IB2006/003950 of 19 December 2006 (WO 2007/083191) entitled "Multiple-input and multiple-output amplifier", in the French patent application number 06/05633 of 23 June 2006 entitled "Amplificateur à entrées multiples et sorties multiples utilisant l'induction mutuelle dans le réseau de rétroaction", and in the corresponding international application number PCT/IB2007/001344 of 26 April 2007 (WO 2008/001168) entitled "Multiple-input and multiple-output amplifier using mutual induction in the feedback network".

The multiple-input-port and multiple-output-port amplifier may comprise a multiple-input and multiple-output series-series feedback amplifier having pseudo-differential inputs, for instance described in the French patent application number 08/03982 of 11 July 2008, entitled "Amplificateur à entrées multiples et sorties multiples ayant des entrées pseudo-différentielles" and in the corresponding international application number PCT/IB2009/051358 of 31 March 2009 (WO 2010/004445) entitled "Multiple-input and multiple-output amplifier having pseudo-differential inputs".

## 20 BRIEF DESCRIPTION OF THE DRAWINGS

10

15

25

30

Other advantages and characteristics will appear more clearly from the following description of particular embodiments of the invention, given by way of non-limiting examples, with reference to the accompanying drawings in which:

- Figure 1 shows the coupling devices of a near-field chip-to-chip multichannel transmission system, and has already been discussed in the section dedicated to the presentation of prior art;

- Figure 2 shows the block-diagram of a first example of a transmitter for a near-field chip-to-chip multichannel transmission system, and has already been discussed in the section dedicated to the presentation of prior art;

- Figure 3 shows the block-diagram of a second example of a transmitter for a near-field chip-to-chip multichannel transmission system, and has already been discussed in the section dedicated to the presentation of prior art;

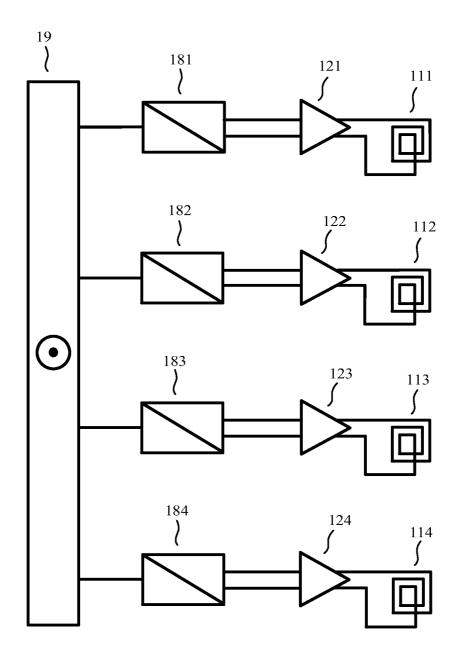

- Figure 4 shows the block diagram of a first embodiment of the invention;

- Figure 5 shows the block diagram of a second embodiment of the invention.

#### DETAILED DESCRIPTION OF SOME EMBODIMENTS

## First embodiment.

5

25

30

As a first embodiment of a device of the invention, given by way of non-limiting example, we have represented in Fig. 4 the block diagram of a transmitter for near-field chip-to-chip multichannel transmission providing m = 4 transmission channels for digital transmission from a first monolithic integrated circuit to a second monolithic integrated circuit, comprising: n = 4 coupling devices (111) (112) (113) (114) built in the first monolithic integrated circuit, each of said coupling devices being a planar winding sensitive to magnetic field variations;

a multiple-input-port and multiple-output-port amplifier (13) built in the first monolithic integrated circuit, said multiple-input-port and multiple-output-port amplifier having *m* input ports and *n* output ports, each of said output ports being connected to one and only one of said coupling devices (111) (112) (113) (114), each of said coupling devices (111) (112) (113) (114) being connected to one and only one of said output ports, said multiple-input-port and multiple-output-port amplifier having, when said multiple-input-port and multiple-output-port amplifier is in the activated state, for small signals, at each frequency in a frequency band used for transmission, a short-circuit transfer admittance matrix, said short-circuit transfer admittance matrix being a complex matrix of size  $n \times m$ , two or more entries of each row of said short-circuit transfer admittance matrix being significantly different from zero;

m signal shaping circuits (181) (182) (183) (184), each of said signal shaping circuits having an input port connected to the source (19), each of said signal shaping circuits having an output port connected to one of the input ports of the multiple-input-port and multiple-output-port amplifier (13).

The transmitter shown in Fig. 4 is a part of a near-field multichannel transmission system which also comprises a receiver comprising n coupling devices built in the second monolithic integrated circuit, each of these coupling devices being a planar winding sensitive to magnetic field variations. All interactions between said 2n coupling devices built in the first monolithic integrated circuit and in the second monolithic integrated circuit are described by the following equations:

$$\mathbf{V}_{O} = -j\boldsymbol{\omega} \left( \mathbf{L}_{T} \mathbf{I}_{O} + \mathbf{L}_{C} \mathbf{I}_{R} \right) - \mathbf{R}_{T} \mathbf{I}_{O}$$

(3)

$$\mathbf{V}_{R} = -j\boldsymbol{\omega} \left( {}^{t}\mathbf{L}_{C}\mathbf{I}_{O} + \mathbf{L}_{R}\mathbf{I}_{R} \right) - \mathbf{R}_{R}\mathbf{I}_{R}$$

(4)

where  $\omega$  is the radian frequency, where  $\mathbf{L}_T$ ,  $\mathbf{L}_C$ ,  $\mathbf{L}_R$ ,  $\mathbf{R}_T$  and  $\mathbf{R}_R$  are square  $n \times n$  real matrices, where  ${}^t\mathbf{X}$  denotes the transpose of a matrix  $\mathbf{X}$ , where  $\mathbf{I}_R$  is the column-vector of the currents

delivered by the coupling devices built in the second monolithic integrated circuit, where  $V_R$  is the column-vector of the voltages across the coupling devices built in the second monolithic integrated circuit, and where  $V_O$  and  $I_O$  are defined above.

All entries of the matrices  $\mathbf{L}_T$ ,  $\mathbf{L}_C$  and  $\mathbf{L}_R$  have the dimensions of inductance. All entries of the matrices  $\mathbf{R}_T$  and  $\mathbf{R}_R$  have the dimensions of resistance. The first monolithic integrated circuit and the second monolithic integrated circuit being structurally combined, the specialist understands that it is possible to compute the matrices  $\mathbf{L}_T$ ,  $\mathbf{L}_C$ ,  $\mathbf{L}_R$ ,  $\mathbf{R}_T$  and  $\mathbf{R}_R$ . In this first embodiment, the designer uses a multiple-input-port and multiple-output-port amplifier such that all entries of  $\mathbf{Y}_O$ ,  $\mathbf{Y}_R$  and  $\mathbf{Y}_I$  have a small absolute value in the frequency band used for transmission, so that the voltages across the coupling devices built in the second monolithic integrated circuit are approximately given by

$$\mathbf{V}_{R} = -j\omega \left( {}^{t}\mathbf{L}_{C}\mathbf{Y}_{T}\mathbf{V}_{I} + \mathbf{L}_{R}\mathbf{I}_{R} \right) - \mathbf{R}_{R}\mathbf{I}_{R}$$

(5)

The designer uses a receiver presenting a high impedance to each of the coupling devices built in the second monolithic integrated circuit. Thus, the specialist understands that the set of the short-circuit transfer admittance matrices which can each cancel the crosstalk between the voltages across the coupling devices built in the second monolithic integrated circuit is defined by the condition

$$\mathbf{Y}_{T} \approx {}^{t}\mathbf{L}_{C}^{-1}\mathbf{D} \tag{6}$$

where **D** is a diagonal complex matrix, **D** being arbitrary and possibly frequency-dependent. Thus, the designer may design a multiple-input-port and multiple-output-port amplifier such that said short-circuit transfer admittance matrix is the product of a frequency-independent real matrix and a diagonal matrix. A suitable short-circuit transfer admittance matrix may be obtained using a multiple-input and multiple-output series-series feedback amplifier or a multiple-input and multiple-output series-series feedback amplifier having pseudo-differential inputs. Thus, the multiple-input-port and multiple-output-port amplifier may use a feedback providing, at each frequency in said frequency band used for transmission, a short-circuit transfer admittance matrix such that two or more entries of each row of said short-circuit transfer admittance matrix are significantly different from zero.

## Second embodiment.

10

15

20

25

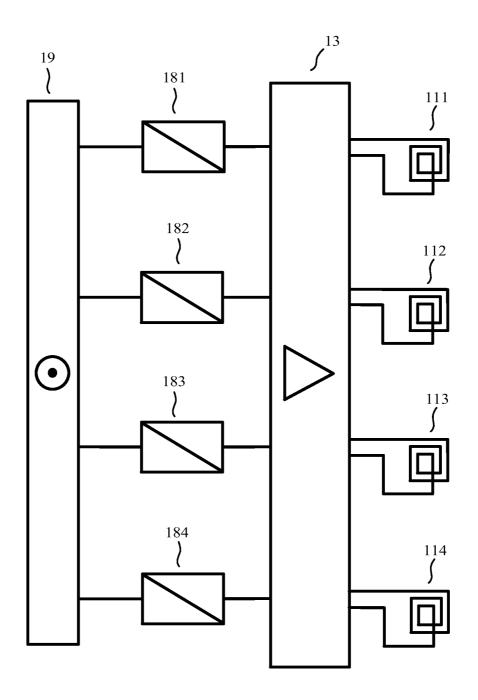

As a second embodiment of a device of the invention, given by way of non-limiting example, we have represented in Fig. 5 the block diagram of a transmitter for near-field chip-to-chip multichannel transmission providing m = 4 transmission channels for digital transmission from a first monolithic integrated circuit to a second monolithic integrated circuit, comprising:

5

10

20

25

30

35

n = 4 coupling devices (111) (112) (113) (114) built in the first monolithic integrated circuit, each of said coupling devices being a conducting surface sensitive to electric field variations;

a multiple-input-port and multiple-output-port amplifier (13) built in the first monolithic integrated circuit, said multiple-input-port and multiple-output-port amplifier having *m* input ports and *n* output ports, each of said output ports being connected to one and only one of said coupling devices (111) (112) (113) (114), each of said coupling devices (111) (112) (113) (114) being connected to one and only one of said output ports, said multiple-input-port and multiple-output-port amplifier having, when said multiple-input-port and multiple-output-port amplifier is in the activated state, for small signals, at each frequency in a frequency band used for transmission, a short-circuit transfer admittance matrix, said short-circuit transfer admittance matrix being a complex matrix of size  $n \times m$ , two or more entries of each row of said short-circuit transfer admittance matrix being different from zero;

m signal shaping circuits (181) (182) (183) (184), each of said signal shaping circuits having an input port connected to the source (19), each of said signal shaping circuits having an output port connected to one of the input ports of the multiple-input-port and multiple-output-port amplifier (13).

The transmitter shown in Fig. 5 is a part of a near-field multichannel transmission system which also comprises a receiver comprising n coupling devices built in the second monolithic integrated circuit, each of these coupling devices being a conducting surface sensitive to electric field variations. All interactions between the 2n coupling devices built in the first monolithic integrated circuit and in the second monolithic integrated circuit are described by the following equations:

$$\mathbf{I}_{O} = -j\boldsymbol{\omega} \left( \mathbf{C}_{T} \mathbf{V}_{O} + \mathbf{C}_{C} \mathbf{V}_{R} \right) \tag{7}$$

$$\mathbf{I}_{R} = -j\omega \left( {}^{t}\mathbf{C}_{C}\mathbf{V}_{O} + \mathbf{C}_{R}\mathbf{V}_{R} \right) \tag{8}$$

where  $\mathbf{C}_T$ ,  $\mathbf{C}_C$  and  $\mathbf{C}_R$  are square  $n \times n$  real matrices, where  $\mathbf{I}_R$  is the column-vector of the currents delivered by the coupling devices built in the second monolithic integrated circuit, where  $\mathbf{V}_R$  is the column-vector of the voltages across the coupling devices built in the second monolithic integrated circuit, and where  $\mathbf{V}_O$  and  $\mathbf{I}_O$  are defined above.

All entries of the matrices  $C_T$ ,  $C_C$  and  $C_R$  have the dimensions of capacitance. The first monolithic integrated circuit and the second monolithic integrated circuit being structurally combined, the specialist understands that it is possible to compute the matrices  $C_T$ ,  $C_C$  and  $C_R$ . In this second embodiment, the designer uses a multiple-input-port and multiple-output-port amplifier such that all entries of  $Y_O$ ,  $Y_R$  and  $Y_I$  have a small absolute value in the frequency band used for transmission, so that the currents delivered by the coupling devices built in the

second monolithic integrated circuit are approximately given by

$$\mathbf{I}_{R} = {}^{t}\mathbf{C}_{C}\mathbf{C}_{T}^{-1}\mathbf{Y}_{T}\mathbf{V}_{I} + j\omega\left({}^{t}\mathbf{C}_{C}\mathbf{C}_{T}^{-1}\mathbf{C}_{C} - \mathbf{C}_{R}\right)\mathbf{V}_{R}$$

(9)

The designer uses a receiver presenting a low impedance to each of the coupling devices built in the second monolithic integrated circuit. Thus, the specialist understands that the set of the short-circuit transfer admittance matrices which can each cancel the crosstalk between the currents delivered by the coupling devices built in the second monolithic integrated circuit is defined by the condition

$$\mathbf{Y}_{T} \approx \mathbf{C}_{T}^{-1} \mathbf{C}_{C}^{-1} \mathbf{D} \tag{10}$$

where **D** is a diagonal complex matrix, **D** being arbitrary and possibly frequency-dependent. Thus, the designer may design a multiple-input-port and multiple-output-port amplifier such that said short-circuit transfer admittance matrix is the product of a frequency-independent real matrix and a diagonal matrix. A suitable short-circuit transfer admittance matrix may be obtained using a multiple-input and multiple-output series-series feedback amplifier or a multiple-input and multiple-output series-series feedback amplifier having pseudo-differential inputs.

## Third embodiment.

5

10

15

20

25

30

A third embodiment of a device of the invention, given by way of non-limiting example, also corresponds to the block diagram of a transmitter for near-field chip-to-chip multichannel transmission shown in Fig. 5. What has been said above about the second embodiment is applicable to this third embodiment except that, in this third embodiment,  $\mathbf{Y}_O$  is equal to a diagonal real matrix denoted by  $\mathbf{G}_O$  such that the absolute value of each diagonal entry of  $\mathbf{G}_O$  is much greater than the absolute values of all entries of  $j\omega$   $\mathbf{C}_T$ , in the frequency band used for transmission. This is because drivers having a low output impedance are used as output stage of the multiple-input-port and multiple-output-port amplifier. Thus, the currents delivered by the coupling devices built in the second monolithic integrated circuit are approximately given by

$$\mathbf{I}_{R} = j\omega \left( {}^{t}\mathbf{C}_{C}\mathbf{G}_{O}^{-1}\mathbf{Y}_{T}\mathbf{V}_{I} - \mathbf{C}_{R}\mathbf{V}_{R} \right)$$

(11)

The designer uses a receiver presenting a low impedance to each of the coupling devices built in the second monolithic integrated circuit. Thus, the specialist understands that the set of the short-circuit transfer admittance matrices which can each cancel the crosstalk between the

currents delivered by the coupling devices built in the second monolithic integrated circuit is defined by the condition

$$\mathbf{Y}_{T} \approx \mathbf{G}_{O}^{t} \mathbf{C}_{C}^{-1} \mathbf{D} \tag{12}$$

where **D** is a diagonal complex matrix, **D** being arbitrary and possibly frequency-dependent. Thus, the designer may design a multiple-input-port and multiple-output-port amplifier such that said short-circuit transfer admittance matrix is the product of a frequency-independent real matrix and a diagonal matrix. A suitable short-circuit transfer admittance matrix may be obtained using a multiple-input and multiple-output series-series feedback amplifier or a multiple-input and multiple-output series-series feedback amplifier having pseudo-differential inputs.

## Fourth embodiment (best mode).

5

10

15

20

25

30

In a fourth embodiment of a device of the invention, given by way of non-limiting example and best mode of carrying out the invention, a transmitter for near-field chip-to-chip multichannel transmission providing m transmission channels each corresponding to a binary signal to be sent from a first monolithic integrated circuit to a second monolithic integrated circuit, where m is an integer greater than or equal to 2, comprises:

n = m coupling devices built in the first monolithic integrated circuit, each of said coupling devices being a multilayer winding sensitive to magnetic field variations;

a multiple-input-port and multiple-output-port circuit built in the first monolithic integrated circuit, said multiple-input-port and multiple-output-port circuit having *n* output ports, each of said output ports being connected to one and only one of said coupling devices, each of said coupling devices being connected to one and only one of said output ports, said multiple-input-port and multiple-output-port circuit being such that each of said coupling devices is subject to a current determined by two or more of said binary signals to be sent.

Let us number said binary signals from 1 to m. Let us also number said coupling devices from 1 to m. For an integer j greater than or equal to 1 and less than or equal to m, the multiple-input-port and multiple-output-port circuit receives the original signal  $X_j$  and the complementary signal  $\overline{X}_j$ . The original signal  $X_j$  is applied to the gate of an insulated gate field-effect transistor of the multiple-input-port and multiple-output-port circuit. The drain of this insulated gate field-effect transistor is coupled to the coupling device number j, and no current flows through this drain when  $X_j = 0$ . The complementary signal  $\overline{X}_j$  is applied to the gate of one or more other insulated gate field-effect transistors of the multiple-input-port and multiple-output-port circuit. The drain of each of said one or more other insulated gate field-effect transistors is coupled to

a coupling device other than the coupling device number j and no current flows through these drains when  $\overline{X}_j = 0$ . Each coupling device being coupled to the drain of at least one insulated gate field-effect transistors to the gate of which a complementary signal is applied, each coupling device is subject to a current determined by two or more of the binary signals to be sent. The specialist understands that the channel widths of the insulated gate field-effect transistors can be proportioned such that the crosstalk between the voltages across the coupling devices built in the second monolithic integrated circuit internal is canceled.

The specialist understands that, in this fourth embodiment, the multiple-input-port and multiple-output-port circuit does not operate as a linear circuit. Thus, this fourth embodiment does not comprise a multiple-input-port and multiple-output-port amplifier for which a meaningful short-circuit transfer admittance matrix may be defined. This fourth embodiment reduces internal crosstalk and has a low power consumption.

#### INDICATIONS ON INDUSTRIAL APPLICATIONS

10

15

20

25

30

The transmitter for near-field chip-to-chip multichannel transmission of the invention can be used as a transmitter in the capacitive or inductive links used for vertical signal transmission between the stacked chips of a system-in-package using three-dimensional integration.

In the first, second and third embodiments of a device of the invention presented above, the transmitter for near-field chip-to-chip multichannel transmission of the invention provides m = 4 transmission channels. This is not at all a characteristic of the invention. A transmitter for near-field chip-to-chip multichannel transmission of the invention may provide a large number of transmission channels.

The transmitter for near-field chip-to-chip multichannel transmission of the invention is suitable for sending analog signals and/or digital signals. The transmitter for near-field chip-to-chip multichannel transmission of the invention is suitable for sending signals using any type of modulation.

The transmitter for near-field chip-to-chip multichannel transmission of the invention has the advantage of reducing crosstalk between the transmission channels, over a wide bandwidth. The transmitter for near-field chip-to-chip multichannel transmission of the invention has the advantage of increasing the number of transmission channels which may be created in a given area. The transmitter for near-field chip-to-chip multichannel transmission of the invention has the advantage of increasing the transmission distance which may be obtained in a given area.

#### **CLAIMS**

- 1. A transmitter of a near-field multichannel transmission system providing m transmission channels each corresponding to a signal to be sent from a first monolithic integrated circuit to a second monolithic integrated circuit, where m is an integer greater than or equal to 2, the first monolithic integrated circuit and the second monolithic integrated circuit being structurally combined, the transmitter comprising n coupling devices (111) (112) (113) (114) built in the first monolithic integrated circuit, where n is an integer greater than or equal to m, each of said coupling devices being subject to an electrical variable determined by two or more of said signals to be sent.

- 2. The transmitter of claim 1, wherein one or more of said coupling devices (111) (112) (113) (114) is sensitive to electric field variations.

- 3. The transmitter of any of the claims 1 or 2, wherein one or more of said coupling devices (111) (112) (113) (114) is sensitive to magnetic field variations.

- 4. The transmitter of any of the claims 1 to 3, further comprising a multiple-input-port and multiple-output-port amplifier (13), said multiple-input-port and multiple-output-port amplifier being built in the first monolithic integrated circuit, said multiple-input-port and multiple-output-port amplifier having *m* input ports and *n* output ports, each of said output ports being connected to one and only one of said coupling devices, each of said coupling devices being connected to one and only one of said output ports, said multiple-input-port and multiple-output-port amplifier having, when said multiple-input-port and multiple-output-port amplifier is in the activated state, for small signals, at each frequency in a frequency band used for transmission, a short-circuit transfer admittance matrix, said short-circuit transfer admittance matrix being a complex matrix of size *n* × *m*, two or more entries of each row of said short-circuit transfer admittance matrix being different from zero.

- 5. The transmitter of claim 4, wherein, at each frequency in said frequency band used for transmission, in each row of said short-circuit transfer admittance matrix, at least one entry different from an entry having the greatest absolute value has an absolute value greater than 1/100 times the absolute value of said entry having the greatest absolute value.

- 6. The transmitter of any of the claims 4 or 5, wherein said short-circuit transfer admittance matrix is the product of a frequency-independent real matrix and a diagonal matrix.

- 7. The transmitter of any of the claims 4 to 6, wherein the multiple-input-port and multiple-output-port amplifier (13) uses a feedback providing, at each frequency in said frequency band used for transmission, a short-circuit transfer admittance matrix such that two or more entries of each row of said short-circuit transfer admittance matrix are significantly different from zero.

- 8. The transmitter of any of the claims 4 to 7, wherein the multiple-input-port and multiple-output-port amplifier (13) comprises a multiple-input and multiple-output series-series feedback amplifier.

- 9. The transmitter of any of the claims 4 to 8, wherein the multiple-input-port and multiple-output-port amplifier (13) comprises a multiple-input and multiple-output series-series feedback amplifier having pseudo-differential inputs.

10

15

10. The transmitter of any of the claims 1 to 9, wherein said n coupling devices (111) (112) (113) (114) are used for receiving an electric field and/or a magnetic field, as parts of a near-field transmission system providing one or more transmission channels each corresponding to a signal to be sent from the second monolithic integrated circuit to the first monolithic integrated circuit.

F16.1

FIG. 2

FIG. 3

FIG. 4

**FIG. 5**

## INTERNATIONAL SEARCH REPORT

International application No PCT/IB2012/052709

Relevant to claim No.

A. CLASSIFICATION OF SUBJECT MATTER INV. H01L25/065 H04B5/00 ADD.

According to International Patent Classification (IPC) or to both national classification and IPC

#### B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)  $H01L \quad H04B$

Category\*

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

Citation of document, with indication, where appropriate, of the relevant passages

EPO-Internal, INSPEC, WPI Data

C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Y                                                                                                                                                                                | YOSHIDA Y ET AL: "A 2 Gb/s Bi-I Inter-Chip Data Transceiver With Differential Inductors for High Inductive Channel Array", IEEE JOURNAL OF SOLID-STATE CIRC SERVICE CENTER, PISCATAWAY, NJ, vol. 43, no. 11, 1 November 2008 (2008-11-01), pa 2363-2369, XP011238708, ISSN: 0018-9200, DOI: 10.1109/JSSC.2008.2004530 cited in the application the whole document | n<br>Density<br>CUITS, IEEE<br>USA,                                                                                                                                                                                                                                        | 1,3,10<br>4-9                |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--|--|--|--|

| Turther documents are listed in the continuation of Box C.  X See patent family annex.                                                                                           |                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                            |                              |  |  |  |  |

| "A" docume<br>to be o<br>"E" earlier a                                                                                                                                           | ategories of cited documents :  nt defining the general state of the art which is not considered f particular relevance pplication or patent but published on or after the international                                                                                                                                                                          | "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention  "X" document of particular relevance; the claimed invention cannot be |                              |  |  |  |  |

| filing da                                                                                                                                                                        | ate<br>nt which may throw doubts on priority_claim(s) or which is                                                                                                                                                                                                                                                                                                 | considered novel or cannot be considered step when the document is taken alon                                                                                                                                                                                              | ered to involve an inventive |  |  |  |  |

| cited to establish the publication date of another citation or other special reason (as specified)  "O" dooument referring to an oral disclosure, use, exhibition or other means |                                                                                                                                                                                                                                                                                                                                                                   | "Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art                           |                              |  |  |  |  |

| "P" document published prior to the international filing date but later than the priority date claimed                                                                           |                                                                                                                                                                                                                                                                                                                                                                   | "&" document member of the same patent family                                                                                                                                                                                                                              |                              |  |  |  |  |

| Date of the a                                                                                                                                                                    | octual completion of the international search                                                                                                                                                                                                                                                                                                                     | Date of mailing of the international sea                                                                                                                                                                                                                                   | rch report                   |  |  |  |  |

| 27                                                                                                                                                                               | 7 July 2012                                                                                                                                                                                                                                                                                                                                                       | 22/11/2012                                                                                                                                                                                                                                                                 |                              |  |  |  |  |

| Name and m                                                                                                                                                                       | nailing address of the ISA/<br>European Patent Office, P.B. 5818 Patentlaan 2<br>NL - 2280 HV Rijswijk<br>Tel. (+31-70) 340-2040,                                                                                                                                                                                                                                 | Authorized officer Burghardt, Gisela                                                                                                                                                                                                                                       |                              |  |  |  |  |

| Farma DOT/ISA/O                                                                                                                                                                  | Fax: (+31-70) 340-3016  10 (second sheet) (April 2005)                                                                                                                                                                                                                                                                                                            | burgharat, drsera                                                                                                                                                                                                                                                          |                              |  |  |  |  |

## **INTERNATIONAL SEARCH REPORT**

International application No

PCT/IB2012/052709

|            |                                                                                                                                                                                                                                                                                                                              | PCT/IB2012/052709     |  |  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|--|

| C(Continua | tion). DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                                                                                                                                   |                       |  |  |

| Category*  | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                                                                                           | Relevant to claim No. |  |  |

| X          | FAZZI A ET AL: "3-D Capacitive Interconnections for Wafer-Level and Die-Level Assembly", IEEE JOURNAL OF SOLID-STATE CIRCUITS, IEEE SERVICE CENTER, PISCATAWAY, NJ, USA, vol. 42, no. 10, 1 October 2007 (2007-10-01), pages 2270-2282, XP011193060, ISSN: 0018-9200, DOI: 10.1109/JSSC.2007.905230 cited in the application | 1,2,10                |  |  |

| Υ          | paragraph [000I] - paragraph [0III];<br>figures 1,2,4<br>paragraph [000V]                                                                                                                                                                                                                                                    | 4-9                   |  |  |

| Y          | WO 2010/004445 A1 (EXCEM [FR]; BROYDE FREDERIC [FR]; CLAVELIER EVELYNE [FR]) 14 January 2010 (2010-01-14) cited in the application page 3, line 20 - page 9, line 5; figure 1                                                                                                                                                | 4-9                   |  |  |

| A          | US 2009/176450 A1 (CHOW ALEX [US] ET AL) 9 July 2009 (2009-07-09) abstract; figures 1,6                                                                                                                                                                                                                                      |                       |  |  |

## **INTERNATIONAL SEARCH REPORT**

Information on patent family members

International application No

PCT/IB2012/052709

| Patent document<br>cited in search report |    | Publication<br>date | Patent family<br>member(s) |                                                            | Publication<br>date                                  |

|-------------------------------------------|----|---------------------|----------------------------|------------------------------------------------------------|------------------------------------------------------|

| WO 2010004445                             | A1 | 14-01-2010          | EP<br>FR<br>US<br>WO       | 2351212 A1<br>2933823 A1<br>2011074502 A1<br>2010004445 A1 | 03-08-2011<br>15-01-2010<br>31-03-2011<br>14-01-2010 |

| US 2009176450                             | A1 | 09-07-2009          | TW<br>US<br>WO             | 201015890 A<br>2009176450 A1<br>2009088869 A2              | 16-04-2010<br>09-07-2009<br>16-07-2009               |